# μPD77C20A, 7720A, 77P20 Digital Signal Processors

### Description

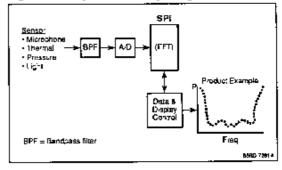

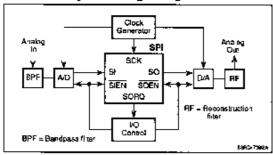

The µPD77C20A, µPD7720A, and µPD77P20—three signal processing interface (SPI) chips that are functionally the same—are advanced architecture microcomputers optimized for signal processing algorithms. Their speed and flexibility allow these SPIs to efficiently implement signal processing functions in a wide range of environments and applications.

The 7720A SPI, a revision of the 7720, the original mask. ROM chip, uses a third less power than the 7720.

The 77C20A is a CMOS pin-for-pin compatible version of the NMOS version, 7720A. This advanced architecture CMOS microcomputer has power requirements 80 percent less than the 7720A, making the 77C20A appropriate for portable applications and other designs requiring low power and low heat dissipation.

Minor differences between 7720A and 77C20A are described in the Instruction Timing section.

The 77P20 is an ultraviolet erasable and electrically programmable (EPROM) version of the 7720A. Program and data ROM, masked for the 7720A, are implemented in EPROM for the 77P20. The 77P20 is useful in prototype applications or in systems where product quantities are insufficient for masked ROM development.

Since the inception of 7720 and its companion EPROM version, 77P20, there have been several mask revisions to improve manufacturability and function. A 77P20 must always be used to verify the functions of a user's system before ROM code for 77C20A or 7720A is submitted, but certain early versions of 77P20 must not be used for final verification. Refer to the section on  $\mu$ PD77P20 for details.

## **Features**

- Low-power CMOS: 24 mA typical current use (77C20A)

- Fast instruction execution: 240 ns with 8.333 MHz clock

- 16-bit data word

- Multioperation instructions for fast program execution: multiply, accumulate, move data, adjust memory pointers—all in one instruction cycle

- Modified Harvard architecture with three separate memory areas

Program ROM (512 x 23 bits)

- Data ROM (510 x 13 bits)

- Data RAM (128 x 16 bits)

- 16 x 16-bit multiplier; 31-bit product with every instruction

- □ Dual 16-bit accumulators

- □ External maskable interrupt

- □ Four-level stack for subroutines and/or interrupt

- Multiple I/O capabilities.

- Serial: 8- or 16-bit (480 ns/bit)

Parallel: 8- or 16-bit

- DMA

- - μPD8085

- -- µPD8086/88

- —µPD780 (Z80³)

- ⊆ Single +5-volt power supply

- F NMOS technology (7720A, 77P20)

- Extended temperature range.

### Applications

- Portable telecommunications equipment

- Digital filtering

- High-speed data modems

- Fast Fourier transforms (FFT)

- Speech synthesis and analysis

- Dual-tone multifrequency (DTMF) transmitters/ receivers

- c Equalizers

- Adaptive control

- Numerical processing

### Performance Benchmarks

- Second-order digital filter (biquad): 2.21 μs.

- Sin/cos of angles: 5.16 μs.

- μ/A law to linear conversion: 0.49 μs.

- ⊐ ££T

- 32-point complex: 0.7 ms

- -64-point complex: 1.6 ms

Z50 is a registered trademark of 7trag Corporation.

### Ordering Information

| Part Number        | Package            | Mex<br>Frequency<br>of Operation | Normal<br>Temperature<br>Range |

|--------------------|--------------------|----------------------------------|--------------------------------|

| µPD77C20AC         | 28-pin plastic DIP | 6.33 MHz                         | 40 to ∽95°C                    |

| ALK                | 29-pir: PLCC       |                                  |                                |

| A_                 | 44-pir. PLCC       | -                                |                                |

| AGW                | 32-pin 80°         | -                                |                                |

| μ <b>PD7720A</b> C | 28-pin plastic UIP | 8.33 MHz                         | -10 to -70°C                   |

| μPD77P20D          | 28-pin cerdip      | 8.196 MHs                        | 10 te <b>~</b> 70°C            |

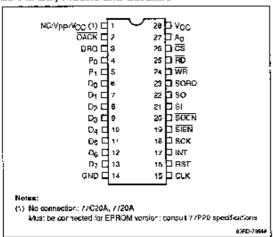

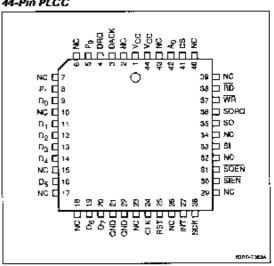

### Pin Configurations

#### 28-Pin DIP, Plastic and Ceramic

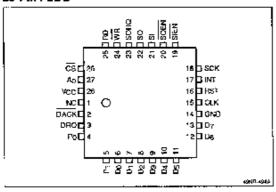

### 28-Pin PLCC

### 32-Pin SOP

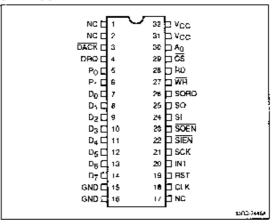

#### 44-Pin PLCC

#### Pin Identification

| Symbol                              | Function                                                      |

|-------------------------------------|---------------------------------------------------------------|

| A <sub>0</sub>                      | Status/dota register select imput                             |

| CLK                                 | Single-phase master clock input                               |

| <del>C</del> 8                      | Chip select input                                             |

| D <sub>0</sub> -D <sub>7</sub>      | Three-state I/O date bus                                      |

| DACK                                | CMA request acknowledge Input                                 |

| CAG                                 | GMA request output                                            |

| INT                                 | Interrupt input                                               |

| P <sub>0</sub> , P <sub>1</sub>     | Goneral-purpose output control lines                          |

| FJ                                  | Read control signal input                                     |

| RST .                               | Reset input                                                   |

| SCK                                 | Serial data I/O clock input                                   |

| SI                                  | Serial data input                                             |

| SIEN                                | Serial input enable input                                     |

| 80                                  | Three-state serial cata output                                |

| SOEN                                | Serial output enable input                                    |

| SORO                                | Sarial data output request                                    |

| WA                                  | Walle central signal input                                    |

| GND                                 | Ground                                                        |

| Vec                                 | -5 V power supply                                             |

| NG/V <sub>PP</sub> /V <sub>CC</sub> | No connection (77O2DA, 772DA)/<br>programming voltage (77P2C) |

### PIN FUNCTIONS

## A<sub>0</sub> (Status/Data Register Select)

This input selects data register for read/write (low) or status register for read (high).

#### CLK

This is the single-phase master clock input.

## CS (Chip Select)

This input enables data transfer through the data port with  $\widehat{RD}$  or  $\overline{WR}.$

### D<sub>0</sub>-D<sub>7</sub> (Data Bus)

This three-state I/O data bus transfers data between the data register or status register and the external data bus.

# DACK (DMA Request Acknowledge)

This input indicates to the SPI that the data bus Is ready for a DMA transfer (DACK = CS and  $A_0$  = 0).

### **DRQ (DMA Request)**

This output signals that the SPI is requesting a data transfer on the data bus,

#### INT (Interrupt)

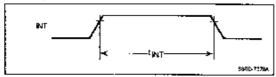

A low-to-high transition on this pin executes a call instruction to location 100H if interrupts were previously enabled.

#### Po, P1

These pins are general-purpose output control lines.

### RD (Read Control Signal)

This input latches data from the data or status register to the data port where it is read by an external device.

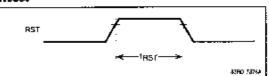

#### RST (Reset)

This input initializes the SPI internal logic and sets the PC to  $\theta_{\rm c}$

### SCK (Serial Data I/O Clock)

When this input is high, a serial data bit is transferred.

### SI (Serial Data Input)

This pin inputs 8- or 16-bit serial data words from an external device such as an A/D converter.

### SIEN (Serial Input Enable)

This input enables the shift clock to the serial input register.

### SO (Serial Data Output)

This three-state port outputs 8- or 16-bit date words to an external device such as a D/A converter.

### SOEN (Serial Output Enable)

This imput enables the shift clock to the serial output register.

### SORO (Serial Data Output Request)

This output specifies to an external device that the serial data register has been loaded and is ready for output. SORQ is reset when the entire 8- or 16-bit word has been transferred.

# WR (Write Control Signal)

This input writes data from the data port into the data register.

### GND

This is the connection to ground.

### Vcc (Power Supply)

This pin is the +5-voit power supply,

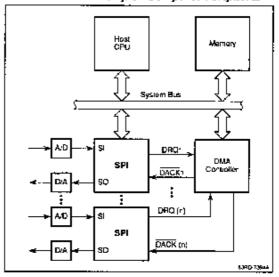

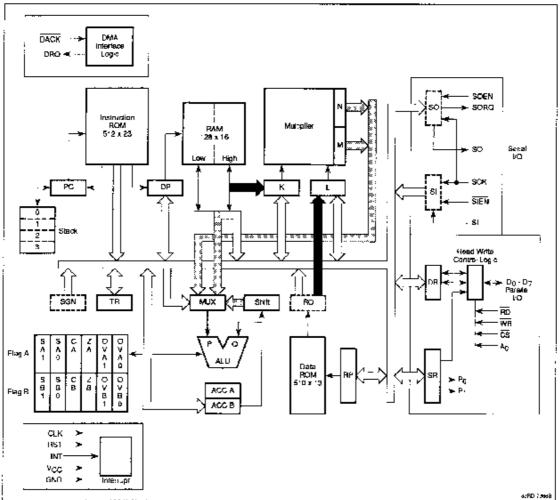

## **Block Diagram**

## NC/V<sub>PP</sub>/V<sub>CC</sub>

This pin is not internally connected in the 77C20A and 7720A. In the 77P20, this pin inputs the programming voltage (V<sub>PP</sub>) when the part is being programmed.

This pin must be connected to  $V_{\rm CC}$  for proper 77P20 operation. Consult the section on the pPD77P20 for details.

#### **FUNCTIONAL DESCRIPTION**

The primary bus (unshaded in the block diagram) makes a data path between all of the registers (including I/O), memory, and the processing sections. This bus is referred to as the IDB (internal data bus). The multiplier input registers K and L can be loaded not only from the IDB bur alternatively via buses (darkened in the block diagram) directly from RAM to the K register and directly from data ROM to the L register. Output from the multiplier in the M and N registers is typically added via buses (shaded in the block diagram) to either accumulator A or B as part of a multioperation instruction.

The SPI is a complete 16-bit microcomputer on a single chip. ROM space provides program and coefficient storage; the on-chip RAM may be used for temporary data, coefficients, and results. A 16-bit arithmetic/logic unit (ALU) and a separate 16 x 16-bit, fully-parallel multiplier provide computational power. This combination allows the implementation of a "sum of products" operation in a single 240-ns instruction cycle. In addition, each arithmetic instruction allows a number of data movement operations to further increase throughout.

Two serial I/O ports interface to codecs and other serial-oriented devices; a parallel port provides both data and status information to conventional microprocessors. Handshaking signals, including DMA controls, allow the SPI to act as a sophisticated programmable perlipheral as well as a standalone microcomputer.

#### MEMORY

Memory is divided into three types: Instruction ROM, data ROM, and data RAM. The 512 x 23-bit words of instruction ROM are addressed by a 9-bit program counter that can be modified by an external reset, interrupt, call, jump, or return instruction.

The data ROM is organized in \$10 x 13-bit words that are addressed through a 9-bit ROM pointer (RP register). The RP may be modified simultaneously with arithmetic instructions so that the next value is available for the next instruction. The data ROM is ideal for storing the necessary coefficients, conversion tables, and other constants for your processing needs.

Do not use data ROM locations 0 and 1 in the 77C20A or 7720A. These locations are reserved for storage of test pattern data. (When submitting code, set these locations to 0). Note that 77P20 allows use of these locations, but using them is not advised.

The data RAM is 128 x 16-bit words and is addressed through a 7-bit data pointer (DP register). The DP has extensive addressing features that operate simultaneously with arithmetic instructions, eliminating additional time for addressing or address modification.

#### **ARITHMETIC CAPABILITIES**

One of the unique features of the SPI's architecture is its arithmetic facilities. With a separate multiplier, ALU, and multiple internal data paths, the SPI is capable of carrying out a multiply, an add, or other arithmetic operation, and a data move between internal registers in a single instruction cycle.

#### AL U

The ALU is a 16-bit two's complement unit capable of executing 16 distinct operations on virtually any of the SPI's internal registers, thus giving the SPI both speed and versatility for efficient data management.

#### Accumulators (ACCA/ACCB)

Associated with the ALU are two 16-bit accumulators, each with its own set of flags, which are updated at the end of each arithmetic instruction (except NOP). Table 1 shows the ACC A/B flag registers. In addition to zero result, sign, carry, and overflow flags, the SPI incorporates auxiliary overflow and sign flags (SA1, SB1, OVA1, OVB1). These flags enable the detection of an overflow condition and maintain the correct sign after as many as three successive additions or subtractions.

Table 1. ACC A/B Flag Registers

| Flag A | SA1 | SAO | CA | ZA | CVA1 | OVAC |

|--------|-----|-----|----|----|------|------|

| Flag B | SBI | SB0 | СВ | Z3 | OVB1 | OVBO |

## Sign Register (SGN)

When OVA1 is set, the SA1 bit will hold the corrected sign of the overflow. The SGN register will use SA1 to automatically generate saturation constants 7FFFH(+) or 8000H(-) to permit efficient limiting of a calculated value. The SGN register is not affected by arithmetic operations on accumulator B, but flags SB1, SB0, CB, ZB, OVB1, and OVB0 are affected.

### Multiplier

Thirty-one bit results are developed by a 16 x 16-bit two's complement multiplier in 240 ns. The result is automatically (atched to two 16-bit registers, M and N, at the end of each instruction cycle. The sign bit and 15 higher bits are in M and the 15 lower bits are in N; the

## μPD77C20A, 7720A, 77P20

LSB in N is zero. A new product is available for use after every instruction cycle, providing significant advantages in maximizing processing speed for real-time signal processing.

#### Stack

The SPI contains a four-level program stack for efficient program usage and interrupt handling.

### Interrupt

The SPI supports a single-level interrupt. Upon sensing a high level on the INT pin, a subroutine call to location 100H is executed. The EI bit of the status register automatically resets to 0, disabling the interrupt facility until it is reenabled under program control.

#### INPUT/OUTPUT

#### General

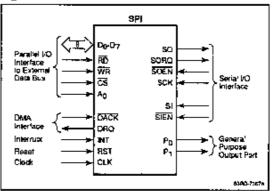

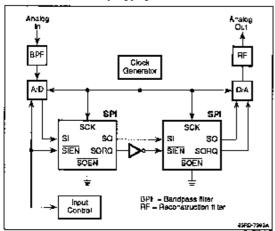

The SPI has three communication ports as shown in tigure 1: two serial and one 8-bit parallel, each with its own control lines for interface handshaking. Parallel port operation is software-configurable to be in either polled mode or DMA mode. A general-purpose, two-line output port rounds out a full complement of interface capability.

#### Serial I/O

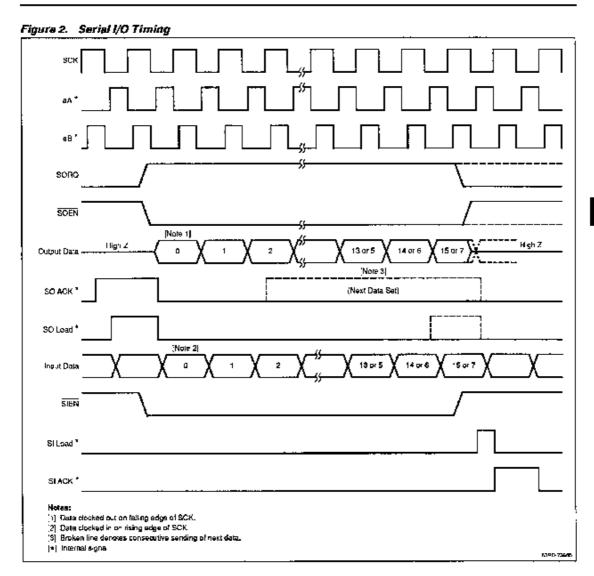

The two shift registers (SI, SO) are software-configurable to single- or double-byte transfers. The shift registers are externally clocked (SCK) to provide a simple interface between the SPI and serial peripherals such as A/D and D/A converters, codecs, or other SPIs. Figure 2 shows serial I/O timing

Figure 1. SPI Communication Ports

## Parallel I/O

The 8-bit parallel I/O port may be used for transferring data or reading the SPI's status as shown in table 2. Data transfer is handled through a 16-bit data register (DR) that is software-configurable for double- or single-byte data transfers. The port is ideally suited for operating with 9080, 9085, and 9086 processor buses and may be used with other processors and computer systems.

## **DMA Mode Option**

Parallel data transfers may be controlled (optionally) via DMA control lines DRQ and DACK. DMA mode allows high-speed transfers and reduced processor overhead. When in DMA mode, DACK input resets DRQ output when data transfer is completed. DACK does not affect any status register bit or flag bit.

Table 2. Parallel R/W Operation

| Ċ\$ | A <sub>0</sub> | WR | ĦΦ | Operation                                                                |

|-----|----------------|----|----|--------------------------------------------------------------------------|

| 1   | х              | Х  | Х  | No affect on Internal operation; D <sub>0</sub> -D <sub>7</sub> are      |

| x   | ×              | 1  | 1  | at high Impedance levels.                                                |

| 0   | 0              | o  | 1  | Data from D <sub>0</sub> -D <sub>7</sub> is bitched to CR<br>(Note 1)    |

| ā   | D              | 1  | 0  | Contents of DR are output to D <sub>0</sub> , D <sub>7</sub><br>(Note 1) |

| a   | 1              | 0  | 1  | lllegal (SR is reed only)                                                |

| a   | 1              | 1  | 0  | Eight MSBs of SR are output to D <sub>0</sub> -D <sub>7</sub>            |

| ā   | Х              | 0  | 0  | lliogal (may not read and write simultaneously)                          |

#### Notes:

(1) Fight MSBs or 8 LSBs of data register (DR) are used, depending on DR status bit (DRS). The condition of DACK - 0 is equivalent to Ag - CS - 0.

#### Status Register

The status register (figure 3) is a 16-bit register in which the eight most significant bits may be read by the system's microprocessor for the latest parallel data I/O status. The RQM and DRS bits can only be affected by parallel data moves, The other bits can be written to (or read) by the SPI's load immediate (LDI) or move (MOV) Instructions. The El bit is automatically reset when an Interrupt is serviced.

Figure 3. Status Register (SR)

| 15  | 14   | 13   | 12  | 11  | 10  | 9            | 8   |

|-----|------|------|-----|-----|-----|--------------|-----|

| PQM | USF1 | USFO | DRS | DMA | DRC | \$0 <b>¢</b> | ŞIC |

| MSB |      |      |     |     |     |              |     |

| 7   | 6    | 5    | 4   | 3   | 2   | 1            | _ 0 |

| EI  | à    | ٥    | ¢   | ٥   | 0   | P1           | PO  |

|     |      |      |     |     |     |              | LSE |

Table 3. Status Register Flags

| Fl≱g                                     | Description                                                                                                                           |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| PQM (Request<br>for Master)              | A read or write from DR to IDB sets RQM = 1. An external read (write) resets RQM = 0.                                                 |

| USF1 and USF0<br>(User Flags 1<br>and 0) | General-purpose flags which may be read by<br>an external processor for user-defined<br>signaling                                     |

| DAS (DA Status)                          | For 16-bit DR transfers (DRC = 0), DRS = 1 after first 8 bits have been transferred, DRS = 0 after all 16 bits have been transferred. |

| DMA (DMA Enable)                         | DMA = 0 (Non-DMA transfer mode) DMA = 1 (DMA transfer mode)                                                                           |

Table 3. Status Register Flags (cont)

| Flag                      | Description                                                                           |

|---------------------------|---------------------------------------------------------------------------------------|

| CAC (DR control)          | DRC = 0 (16-bit mode)<br>DRC = 1 (8-bit mode)                                         |

| SOC (SO Control)          | SOC = 0 (16-bit mode)<br>SOC = 1 (8-bit mode)                                         |

| SIC (SI Contrel)          | SIC = 0 (16-bit mode)<br>SIC ≈ 1 (8-bit mode)                                         |

| El (Enable<br>Interrupt)  | El = 0 (interrupts disabled)<br>El = 1 (interrupts enabled)                           |

| Pa, P1<br>(Parts 0 end 1) | PC and P1 directly control the state of output pins P <sub>0</sub> and P <sub>1</sub> |

#### INSTRUCTIONS

The SPI has three types of instructions: Load Immediate, Branch, and the multifunction OP instruction, Each type takes the form of a 23-bit word and executes in 240 ns.

### Instruction Timing

To control the execution of instructions, the external 8-MHz clock is divided into four phases for Internal execution. The various elements of the 23-bit instruction word are executed in a set order. Multiplication automatically begins first. Also, data moves from source to destination before other elements of the instruction. Data being moved on the internal data bus (IDB) is available for use in ALU operations (if P-select field of the instruction specifies IDB). However, if the accumulator specified in the ASL field is also specified as the destination of the data move, the ALU operation becomes an NOP as the data move supersedes the ALU operation.

Pointer modifications occur at the end of the instruction cycle after their values have been used for data moves. The result of multiplication is available at the end of the instruction cycle for possible use in the next instruction. If a return is specified as part of an OP instruction, it is executed last.

An assembly language OP instruction may consist of what looks like one to six lines of assembly code, but all of these lines are assembled together into one 28-bit instruction word. Therefore, the order of the six lines makes no difference in the order of execution described above. However, for understanding the SPI's operation and to eliminate confusion, write assembly code in the order described; that is, data move, ALU operations, data pointer modifications, and then return.

Minor differences exist between 7720A and 77C20A in internal instruction execution timing. Using normal programming instruction statements, the differences will not appear. However, an instruction such as the following will yield a difference between NMOS and CMOS operation.

#### OP MOV @MEM,B XOR ACCB, RAM

The instruction, which is acceptable using the NEC assembler (AS77201), has an inherent conflict in that data is simultaneously being moved into memory and fetched in one instruction. ALU instructions involving either ACCA or ACCB should not be used. In summary, observe the following rules.

- (1) DST should not be @MEM when PSEL is RAM.

- (2) When SRC is NON, DST must be @NON.

- (3) A should not be used as both DST and ASL.

- (4) B should not be used as both DST AND ASL.

### OP/RT Instruction Field Specification

Figure 4 illustrates the OP/RT instruction field specification. There are two instructions of this type, both of which are capable of executing all ALU functions listed in table 4. The ALU functions operate on the value specified by the P-select field (see table 5). Besides the arithmetic functions, these instructions can also (1) modify the RAM data pointer DP, (2) modify the data ROM pointer RP, and (3) move data along the on-chip data bus from a source register to a destination register. The possible source and destination registers are listed in tables 6 and 7, respectively.

The difference in the two instructions of this type is that RT executes a subroutine or interrupt return at the end of the instruction cycle, but the OP does not. Tables 8, 9, 10, and 11 show the ASL, DPL, DPH, and RPDCR fields, respectively.

Figure 4. OP/RT Instruction Field

| 22 | 21  | 20   | 19     | 18   |     | 15 | 14  | 13 | 12 |

|----|-----|------|--------|------|-----|----|-----|----|----|

| 1  | Ψ   | P-Se | elect  |      | ALU |    | ASL | ΩR | ┖  |

|    | #0P | - 00 | : RT - | - 01 |     |    |     |    |    |

| 11 | ₽     | 8   | 7    |     | 4 | 3 |     | 0 |

|----|-------|-----|------|-----|---|---|-----|---|

| -  | DPH-M | •   |      | SRC |   |   | DST |   |

|    |       | * R | POCA |     |   |   |     |   |

Table 4. ALU Fleid

| 18416 4     |                 |                 | _               |                 |                                      |           |          |        |                       |            |            |

|-------------|-----------------|-----------------|-----------------|-----------------|--------------------------------------|-----------|----------|--------|-----------------------|------------|------------|

| Mnomonic    | D <sub>18</sub> | D <sub>17</sub> | D <sub>16</sub> | D <sub>15</sub> | ALU Function                         | 5A1, \$B1 | 8A0, 980 | CA, CB | <b>ZA</b> , <b>ZB</b> | OVA1, OV81 | OVA0, OVB0 |

| NOP         | a               | 0               | 0               | 0               | No operation                         |           | _        | _      | _                     |            | _          |

| OR          | Q               | 0               | G               | 1               | OR .                                 | ×         | Δ        | D      | Δ                     | ٥          | 0          |

| AND         | D               | 0               | 1               | 0               | AND                                  | ×         | Δ        | D      | Δ                     | Ď          | ۵          |

| XOR         | ٥               | 0               | 1               | 1               | Exclusive OR                         | ×         | Δ        | ٥      | Δ                     | ۵          | ø          |

| au <b>B</b> | 0               | 1               | Q               | ø               | Subtract                             | <u> </u>  | Δ        | Δ      | Δ                     | Δ          | Δ          |

| ADD         | 0               | 1               | 0               | 1               | ADD                                  | Δ         | Δ        | Δ      | Δ                     | Δ          | Δ          |

| SBB         | 0               | 1               | 1               | · •             | Subtrect with borrow                 | Δ         | Δ        | Δ      | Δ                     | ۸          | Δ          |

| ADC         | 0               | 1               | 1               | 1               | Add with carry                       | Δ         | Δ        | Δ      | Δ                     | Δ          | Δ          |

| DEC         | 1               | D               | Q               |                 | Decrement ACC                        | ۵         | 4        | Δ      | Δ                     | Δ          | Δ          |

| INC         | 1               | D               | a               | 1               | Increment ACC                        | Δ         | Δ        | Δ      | Δ                     | V          | Δ          |

| CMP         | 1               | D               | 1               | Û               | Complement ACC<br>(one's complement) | ×         | Δ        | 0      | Δ                     | 0          | 0          |

| SHR1        | 1               | ٥               | 1               | 1               | 1-Bit right shift                    | ×         | Δ        | Λ      | Λ                     | 9          | 0          |

| SHL1        | i               | 1               | ٥               | 0               | 1-Bit lef1 shift                     | ж         | Δ        | Δ      | Ą                     |            | à          |

| SHL2        | 1               | - 2             | ٥               | 1               | 2-Bit left shift                     | х х       | Δ        | 0      | Λ                     | D          | 0          |

| SHL4        | 1               | 1               | 1               | 0               | 4-Bit left shift                     | x         | Δ        | 0      | Δ                     | 0          | C          |

| XCHG        | · <sub>1</sub>  | 1               | 1               | 1               | 6-Bi1 exchange                       | X         | Δ        | 0      | Α                     | 0          | Ď          |

- $\Delta$  . May be affected, depending on the results.

- C Reset

- Pravious status can be held.

Table 5. P-Select Field

| Mnemonic | D <sub>20</sub> | D <sub>19</sub> | ALU Input                  |

|----------|-----------------|-----------------|----------------------------|

| RAM      | 0               | ٥               | RAM                        |

| IDΒ      | 0               | 1               | Internel Data Bus (Note 1) |

| М        | 1               | 0               | M Register                 |

|          | 1               | 1               | N Register                 |

#### Notes:

(1) Any value on the on-chip data bus. Value may be selected from any of the registers listed in table 6 source register selections.

Table 6. SRC Field

| Maemonic | $D_{I}$ | Dē | 05 | D <sub>4</sub> | Source Register           |

|----------|---------|----|----|----------------|---------------------------|

| NON      | ٥       | Ŷ  | 0  | 0              | No register               |

| Α        | ٥       | ٥  | 0  | 1              | AGICA (Accumulator A)     |

| В        | ٥       |    | 1  | Q              | ACCB (Accumulator B)      |

| ТР       | C       | C  | 1  | 1              | TR temporary register     |

| DP       | С       | 1  | 0  | D.             | DP dete pointer           |

| RP       | С       | 1  | 0  | 1              | AP ROM pointer            |

| RØ       | С       | 1  | 1  | Ď              | RO ROM output data        |

| SGN      | ٥       | 1  | 1  | 1              | SGN sign register         |

| PΠ       | 1       | 0  | ٥  | Ó              | DR data register          |

| DRNF     | 1       | 0  | ٥  | 1              | DR no flag (Note 1)       |

| SR       | 1       | C  | 1  | ۵              | SR status register        |

| SIM      | 1       | C  | 1  | 1              | 81 serial in MSB (Note 2) |

| SIL      | 1       | 1  | 0  | 0              | 31 serial in LSB (Note 3) |

| κ        | 1       | 1  | 0  | 1              | K register                |

| L "      | 1       | 1  | 1  | 0              | L register                |

| MEM      | ī       | 1  | 1  | 1              | FAM                       |

### Notes:

- (1) DR to IDB, RQM not set. In DMA, DRO not set.

- (2) First bit in goes to MSB, last bit to LSB,

- (S) First bit gods to LSB, last bit to MSB (bit reversed),

Table 7. DST Field

| Mnemonic | $D_3$ | $D_2$ | D <sub>1</sub> | DD | Destination Register  |

|----------|-------|-------|----------------|----|-----------------------|

| @NON     | Э     | D     | 0              | 0  | No register           |

| GCA.     | a     | Ð     | 0              | 1  | ACCA (Accumulator A)  |

| (%B      | ٥     | ۵     | 1              | C  | ACCB (Accumulator B)  |

| QTR      | 0     | ວ່    | 7              | 1  | TR temporary register |

| @CP      | a     | 1     | 0              | 0  | DP data pointer       |

| @R.P     | a     | 1     | 0              | 1  | RP ROM pointer        |

| @CR      | o     | _1_   | •              | 0  | DR deta ragiater      |

| @SR      | 0     | 1     | •              | 1  | SR status register    |

|          |       |       |                |    |                       |

Table 7. DST Field (cont)

| Mnemonic | $D_3$ | D <sub>2</sub> | D <sub>1</sub> | $\mathbf{p}_0$ | Ocstination Register             |

|----------|-------|----------------|----------------|----------------|----------------------------------|

| @SOL     | 1     | 0              | 0              | 0              | SO serial out LSB (Note 1)       |

| ⊚8ОM     | 1     | 0              | 0              | 1              | SO serial out MSB (Note 2)       |

| @K       | 1     | 0              | 1              | 0              | K (Mult)                         |

| @KLR     | 1     | 0              | 1              | 1              | IDB → K, ROM → L (Note 3)        |

| @KLM     | 1     | ī              | ā              | D              | Hi RAM -> K, .DB → L (Note<br>4) |

| @L       | 1     | 1              | a              | 1              | L (Mult)                         |

| @NON     | 1     | 1              | 1              | 0              | No register                      |

| @МЕМ     | 1     | 1              | 1              | 1              | PAM                              |

#### Notes:

- (1) LSB is fast bit out,

- (2) MSB is first bit out.

- (3) Internal data bus to K, and RCM to L register.

- (4) Contents of RAM address specified by DP<sub>6</sub> = 1, Is placed in K register, IDB is placed in L (that is, 1, DP<sub>5</sub>, DP<sub>4</sub> DP<sub>3</sub>·DP<sub>0</sub>).

Table 8. ASL Field

| Mnemonio | D <sub>14</sub> | ACC Selection |

|----------|-----------------|---------------|

| ADCA     | D               | ACCA          |

| ACCB     | 1               | ACCB          |

## Table 9. DPL Field

| Mnemonic | 013 | D <sub>12</sub> | Low DP Modify (DP <sub>3</sub> -DP <sub>0</sub> ) |

|----------|-----|-----------------|---------------------------------------------------|

| OPNOP    | 0   | 0               | No aperation                                      |

| DPING    | 0   | 1               | frorement DPL                                     |

| DPDEC    | 1   | 0               | Decrement DPL                                     |

| DPCLR    | 1   | 1               | Clear DPL                                         |

### Table 10. DPH Field

| Mnemonic | $D_{11}$ | 010 | Dg | High DP Modify                                                                         |

|----------|----------|-----|----|----------------------------------------------------------------------------------------|

| МО       | 0        | ¢   | J  | Exclusive OR of DPH (DP <sub>6</sub> -DP <sub>4</sub> )                                |

| M1       | 0        | 0   | 1  | with the mask defined by the three bits (D <sub>11</sub> -D <sub>5</sub> ) of the DPH. |

| M2       | a        | 1   | 0  | field bits (b11-5g) of the b: 1:                                                       |

| мэ       | 0        | 1   | 1  |                                                                                        |

| M4       | ,        | G   | 0  |                                                                                        |

| M5       | :        | · c | -  |                                                                                        |

| MS       | 1        | 1   |    |                                                                                        |

| M7       | 1        | 1   | 1  |                                                                                        |

| Table 11. RPDCR Field |

|-----------------------|

|-----------------------|

| Mnemonic | Dg | RP Operation |

|----------|----|--------------|

| RPNOP    | ā  | No operation |

| RPDEC    | 1  | Decrement RP |

### Jump/Call/Branch

Figure 5 shows the JP instruction field specification. Three types of program counter modifications accommodated by the processor are listed in table 12. All the instructions, if unconditional or if the specified condition is true, take their next program execution address from the next address field (NA); otherwise PC = PC + 1.

For the conditional jump Instruction, the condition field specifies the jump condition. Table 13 lists all the instruction mnemonics of the jump/call/branch codes. BRCH or CND values not in table 13 are prohibited.

### Load Data (LDI)

Figure 6 shows the LD instruction field specification. The load data instruction will take the 16-bit value contained in the immediate data field (ID) and place it in the location specified by the destination field (DST). See table 7.

Figure 5. JP Instruction Field

| 2 | 2 |   | 20   | 17 13 | 12 | 4 | 3 | .0 |

|---|---|---|------|-------|----|---|---|----|

|   | 1 | 0 | BRCH | CND   | NA |   |   |    |

| _ |   |   |      |       |    | _ |   |    |

Figure 6. LD Instruction Field

| 22 | 23   | 5 | 3 | 0   |

|----|------|---|---|-----|

| 1  | 1 ID |   | _ | DST |

Table 12. BRCH Field

| D20 | D <sub>19</sub> | D <sub>18</sub> | Branch Instruction |

|-----|-----------------|-----------------|--------------------|

| 1   | Ċ               | ٥ -             | Unconditional jump |

| 1   | Ċ               | 1               | Subroutine call    |

| 0   | 1               | <u> </u>        | Conditional jump   |

#### Table 13. BRCH/CND Fields

| IBBIE 13. | . BHCR/CND Fields |                 |                 |                 |                 |                 |                 |                 |                 |

|-----------|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Mnemonic  | D <sub>20</sub>   | D <sub>19</sub> | D <sub>18</sub> | D <sub>17</sub> | D <sub>16</sub> | D <sub>15</sub> | D <sub>14</sub> | D <sub>13</sub> | Conditions      |

| JMP       | 1                 | 0               | ٥               | 0               | 0               | 0               | ū               | Q               | No condition    |

| CALL      | 1                 | 0               | 1               | 0               |                 | 0               | 0               | 0               | No condition    |

| JNCA      | 0                 | 1               | 0               | 0               | C               | 0               | 0               | ٥               | CA = 0          |

| JCA       | 0                 | 1               | 0               | 0               | D               | Q               | 0               | 1               | CA = 1          |

| JNCB      | 0                 | 1               | ¢               | Q               | Þ               | Q               | 1               | 0               | CB = 0          |

| JCB       | 0_                | 1               | 0               | 0               | 0               | 0               | . 1             | 1               | CB = 1          |

| JNZA      | 0                 | 1               | 0               | Ū               | 0               | 1               | C               | 0               | ZA = 0          |

| JZA       | 0                 | _1_             | ٥               | ¢               | ٥               | 1               | ¢               | 1               | <b>ZA</b> = 1   |

| JNZB      | 0                 | 1               | Q               | 0               | 0               | 1               | 1               | ٥               | ZB = 0          |

| JZB       | 0                 | 1               | ٥               | ¢               | ø               | 3               | 1               | :               | ZB = 1          |

| JNOVAD    | 0                 | 1               | ٥               | ٥               | 1               | 0               | ٥               | 0               | 0.400 = 0       |

| JOVAO     | Ď                 | . 1             | ٥               | Ď               | 1               | ٥               | Û               | ì               | 0VA0 = 1        |

| JNOVB0    | 0                 | 1               | à               | ٥               | 1               | 0               | 1               | 0               | 0VB0 1          |

| JOVBO     | Ď                 | E               | 0               | ٥               | 1               | 0               | 1               | 1               | 0VB0 = 1        |

| JN0VA1    | ٥                 | 7               | Ð               | 0               | ì               | 1               | 0               | 0               | OVA1 - 0        |

| J0VA1     | 0                 | 1               | Ū               | 0               | 1               | 1               | 0               | 1               | 0VA1 - 1        |

| JN0VB1    | 0                 | 1               | D               | 0               | 1               | 1               | 1               | 0               | QVB1 - 0        |

| JOVB1     | 0                 | 1               | O               | 0               | 1               | 1               | 1               | 1               | OVB1 - 1        |

| JNSA0     | 0                 | 1               | D               | 1               | 0               | 0               | 0               | 0               | SAO = D         |

| JSAO      | 0                 | 1               | Þ               | 1               | 0               | ¢               | D               | 1               | SA0 - 1         |

| JNSBo     | 0                 | 1               | D               | 1               | D               | a               | 1               | ø               | <b>SB</b> 0 = 0 |

| Jaba      | 0                 | 1               | Ď               | t               | Ď               | ٥               | 1               | 1               | SB0 = 1         |

| JNSA1     | 0                 | 1               | D               | 1               | 0               | 1               | D               | 0               | SA1 = 0         |

| JBA1      | 0                 | 1               | Ó               | 1               | ٥               | 1               | 0               | 1               | 8AI - 1         |

| JNSB1     | 0                 | 1               | 0               | 1               | ō               | 1               | 1               | a               | SB1 - C         |

| J9B1      | 0                 | 1               | a               | 1               | 0               | 1               | 1               | 1               | 621 - 1         |

| JDPLQ     | 0                 | 1               | 0               | 1               | 1               | 0               | 0               | 0               | DPL = 0         |

| JDPLF     | 0                 | 1               | 0               | 1               | 1               | 0               | 0               | 1               | DPL ~ FH        |

| JNSIAK    | 0                 | 1               | 0               | 1               | 1               | 0               | 1               | 0               | SLACK = 0       |

| JSIAK     | 0                 | 1               | ¢               | 1               | 1               | Q               | 1               | 1               | SLACK = 1       |

| JNISCAK   | 0                 | 1               | 0               | 1               | 1               | -:              | 0               | C               | 50 ACK = 0      |

| JSOAK     | 0                 | 1               | 0               | 1               | 1               | 1               | 0               | 1               | SO ACK = 1      |

| JNRQM     | Ċ                 | •               | 0               | 1               | 1               | 1               | 1               | ٥               | RCM = 0         |

| JRQM      | Ç                 | 1               | 0               | 1               | •               | 1               | 1               | 1               | ROM = 1         |

|           |                   |                 |                 |                 |                 |                 |                 |                 |                 |

### **ELECTRICAL SPECIFICATIONS**

**Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>              |                                |

|----------------------------------------------|--------------------------------|

| 77C20A                                       | -0.5 to ±7.0 V                 |

| 7720A                                        | -0.5 ta ÷7.0 V                 |

| 77P20                                        | -0.3 to ±7.0 V                 |

| Programming voltage, V <sub>PP</sub> (77P20) | -0.3 to ÷22 ∀                  |

| Input voltage, V <sub>I</sub>                |                                |

| 77C20A                                       | $-0.5$ to $V_{\rm CC} + 0.5$ V |

| 7720A                                        | -0.5 to −7.0 V                 |

| 77P20                                        | -0.3 to −7.0 V                 |

| Output voltage, Vo                           |                                |

| 77C20A                                       | 0.5 to V <sub>CC</sub> + 0.5 V |

| 7720A                                        | 0.5 to -7.0 V                  |

| 77P20                                        | ~0.3 to = 7.0 V                |

| Operating temperature, TopT                  |                                |

| 77C20A                                       | 40 to +85°C                    |

| 7720A, 77P20                                 | −10 to <b>−7</b> 0°C           |

| Storage temperature, T <sub>STO</sub>        | -65 to +150°C                  |

Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may effect device reliability.

## Capacitance

| Parameter                 | Symbol          | Min | Max | Unit | Conditions             |

|---------------------------|-----------------|-----|-----|------|------------------------|

| CLK, SCK<br>cepacitence   | οф              |     | 20  | ρF   | f <sub>c</sub> = 1 MHz |

| Input pin<br>capacitance  | C <sub>IN</sub> |     | 10  | pF   |                        |

| Output pin<br>espacitence | Соит            |     | 20  | ₽F   |                        |

## DC Characteristics

$T_A = -10$  to  $\pm 70^{\circ}C$ ;  $V_{CC} = \pm 5$  V  $\pm 5\%$

| Paremeter                   | \$ymbol          | Min          | Тур | Max                   | Unit | Conditions                         |

|-----------------------------|------------------|--------------|-----|-----------------------|------|------------------------------------|

| impul low voltage<br>77C20A | V <sub>IL</sub>  | -0.3         |     | 3.0                   | ٧    |                                    |

| 7720A, 77P20                |                  | -0.5<br>-0.5 |     | 8.0                   | v    |                                    |

| hput high voltage           | VIH              |              |     |                       |      |                                    |

| 77C20A                      |                  | 2.2          |     | V <sub>CC</sub> + 0.3 | ٧    |                                    |

| 7720A, 77P20                |                  | 2.0          |     | $V_{C,C} + 0.5$       | ¥    |                                    |

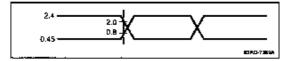

| CLK low voltage             | <sup>γ</sup> φι. |              |     |                       |      |                                    |

| 77C20A                      | , -              | -0.3         |     | 0.45                  | V    |                                    |

| 7720A, 77P20                |                  | -0.5         |     | 0.45                  | ٧    |                                    |

| CLK high voltage            | γфн              |              |     |                       |      |                                    |

| 77C20A                      | F                | 3.5          |     | $V_{CC} + 0.3$        | V    |                                    |

| 77 <b>2</b> 0A, 77P20       |                  | 3.5          |     | V <sub>CC</sub> + 0.5 | V    |                                    |

| Output low voltage          | V <sub>OL</sub>  |              |     | 0.45                  | v    | I <sub>OI</sub> = 2.0 mA           |

| Output high voltage         | Уон              | 24           |     |                       | V    | I <sub>OH</sub> = -400 μA          |

| Input load current          | ILIE             |              |     | 10                    | μА   | V <sub>PV</sub> = 0 V              |

| laput lose ourrent          | l <sub>LIH</sub> | _            |     | 10                    | Aų   | $V_{N} = V_{GC}$                   |

| Output float leaxage        | loc              |              |     | -10                   | Αų   | V <sub>OUT</sub> = 0.47 V          |

| Output float leakage        | l <sub>LOH</sub> |              |     | 10                    | μA   | V <sub>OUT</sub> = V <sub>CC</sub> |

## DC Characteristics (cont)

| Perameter                            | Symbol . | Min | Тур | Mex | Unit | Conditiona                                 |

|--------------------------------------|----------|-----|-----|-----|------|--------------------------------------------|

| Power supply current                 | lcc      |     |     |     |      |                                            |

| 77C23A                               |          |     | 24  | 40  | mΛ   | f <sub>CLK</sub> = 8.192 MHz               |

| 7720A                                |          |     | 120 | 170 | mA   |                                            |

| 77P20                                |          |     | 270 | 350 | mA   |                                            |

| V <sub>PP</sub> current (77P20 only) | lt45     |     |     | 70  | mÅ   | Program mode max pulse<br>purrent (Note 1) |

|                                      |          | 0.5 |     | 3.0 | mA   | Program verify, inhibit (Note 2)           |

### Notes:

(1)  $V_{PP} = 21 \pm 0.5 V$

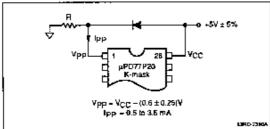

(2) For K-level parts:

For K-level parts:  $V_{PP}$  max =  $(V_{CC} - 0.6 \text{ V}) - 0.25 \text{ V}$   $V_{PP}$  min =  $(V_{CC} - 0.6 \text{ V}) - 0.25 \text{ V}$ For all other step levels:  $V_{PP}$  mex =  $V_{CC} + 0.25 \text{ V}$   $V_{PP}$  min =  $V_{CC} - 0.65 \text{ V}$

# AC Characteristics

$T_{A} = -10$  to  $\pm 70$  °C;  $V_{CC} = \pm 5$  V  $\pm 5\%$

| Parameter                 | Symbol            | Min | Тур                    | Max    | Unit  | Conditions              |

|---------------------------|-------------------|-----|------------------------|--------|-------|-------------------------|

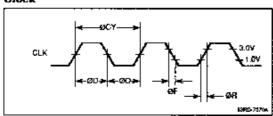

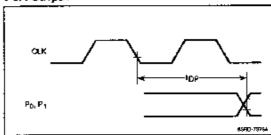

| CLK cycle time            | фсч               |     |                        |        |       |                         |

| 77C20A, 7720A             |                   | 126 |                        | 2000   | ris   |                         |

| 77P20                     |                   | 122 |                        | 2000   | ns    |                         |

| CLK pulse width           | Фロ                | 60  |                        |        | ns ns | Note 4                  |

| CLK rise time             | ΦR                |     |                        | 10     | ra\$  | Note <sub>1</sub> 1     |

| CLK fall time             | Фғ                |     |                        | 13     | រា\$  | Note 1                  |

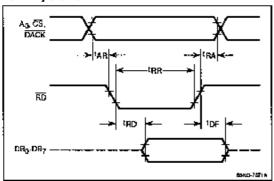

| Address setup time for RD | t <sub>AR</sub>   | 0   | · <del>-</del> · · · · |        | TIE . |                         |

| Address hald time for 🜃   | t <sub>ftA</sub>  | 0   |                        |        | ПВ    |                         |

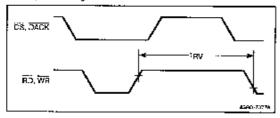

| RD pulse width            | t <sub>BB</sub>   | 250 |                        |        | пв    |                         |

| Data delay from RD        | tao               |     |                        | 150    | ПВ    | C <sub>L</sub> = 100 pF |

| Read to data floating     | tDF               | 10  |                        | 100    | пъ    | G <sub>L</sub> = 100 pF |

| Address setup time for WR | taw               | ٥   |                        |        | па    |                         |

| Address hold time for WR  | FWA.              | 0   |                        |        | пъ    |                         |

| WR pulse width            | 7000              | 250 |                        |        | па    |                         |

| Data setup time for WR    | 1 <sub>DW</sub>   | -50 |                        |        | па    |                         |

| Date held time for WR     | 1wo               | 0   |                        |        | ns    |                         |

| RD. WR. recovery time     | 1 <sub>FW</sub>   | 250 |                        |        | п5    | Note 2                  |

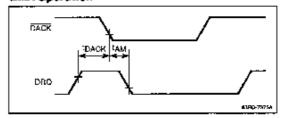

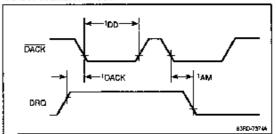

| DRQ delay                 | 1 <sub>AM</sub>   |     |                        | 150    | ns    | C <sub>L</sub> ≃ 100 ∌F |

| DACK delay time           | 1 <sub>DACK</sub> | 1   |                        |        | фФ    | Note 2                  |

| ĎÄČK palse width          |                   |     |                        |        |       | ••                      |

| 77C20A                    |                   | 25C |                        |        |       |                         |

| 772GA                     |                   | 250 |                        | 2030   | F.9   |                         |

| 77P20                     |                   | 250 |                        | 50,000 | D6    |                         |

| SCK cycle time            | †sov              | 480 |                        | DC     | ne    |                         |

| SCK pulse width           | <sup>t</sup> sck  | 230 |                        |        | ne ne |                         |

| SCK rise/lafl time        | tRSC/tFSC         |     | 20                     |        | ПБ    |                         |

## AC Characteristics (cont)

| Parameter                                    | Symbol            | Man | Тур             | Max          | Unit | Conditions              |

|----------------------------------------------|-------------------|-----|-----------------|--------------|------|-------------------------|

| SORQ delay                                   | <sup>†</sup> ORQ  | 30  |                 | 150          | ns   | C <sub>L</sub> = 100 pF |

| SCEN ho'd time                               | toso              | 30  |                 |              | n≤   |                         |

| SOEN setup time                              | tsoc              | 50  |                 |              | па   |                         |

| SO delaty from SCK = low                     | tock              | -   |                 | 150          | D≐   |                         |

| SQ delay from SCK before<br>1st bit (Note 3) | t <sub>DZRQ</sub> | 20  |                 | 300          | ns   | Note 2                  |

| SO delay from SCK                            | tozsc             | 20  | · <del></del> - | 300          | ne - | Note 2                  |

| SO delay for SOEN                            | toze              | 20  |                 | 18C          | n#   | Note 2                  |

| SOEN to SO floating                          | <sup>†</sup> HZE  | 20  |                 | 200          | ne   | Note 2                  |

| SCK to SO floating with<br>SORO high         | t <sub>HZSC</sub> | 20  |                 | 300          | ns   | Note 2                  |

| SO delay from BCK for<br>last bit            | t <sub>hZRO</sub> | 70  |                 | 300          | па   | Note 2                  |

| SIEN, SI setup time                          | t <sub>DC</sub>   | 55  |                 |              | пъ   | Note 2                  |

| SIEN, SI hold time                           | ten               | 30  |                 |              | пв   |                         |

| P <sub>0</sub> , P <sub>1</sub> delay        | top               |     |                 | φ¢γ<br>- 150 | пъ   |                         |

| RST pulse width                              | t <sub>RST</sub>  | 4   |                 |              | фсу  |                         |

| INT pulse width                              | t <sub>INT</sub>  | β   |                 |              | фсү  |                         |

#### Notes:

- (1) Voltage at timing measuring point; 1.0 V and 9.0 V.

- (2) Voltage at seltiming measuring point:  $V_{IL} = V_{OL} = 0.8 \ V \\ V_{IH} = V_{OH} = 2.0 \ V$

- (3) BO goes out of triatate, but date is not valid yet.

- (4) Pulse width Includes CLK rise and fall times. Refer to Clock Timing Waveform.

## **Timing Waveforms**

## Input Waveform of AC Test (except CLK)

### Clock

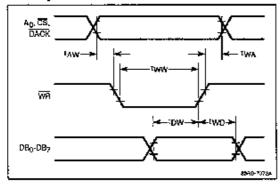

## Read Operation

## Write Operation

## DMA Operation

### 16-Bit Transfer Mode

## Part Output

## Reset

### Timing Waveforms (cont)

#### Read/Write Cycle

#### Interrupt

#### **SERIAL TIMING**

#### Serial Output, Case 1

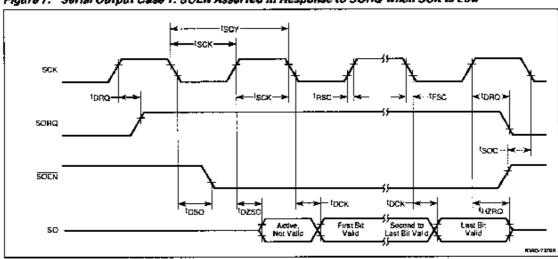

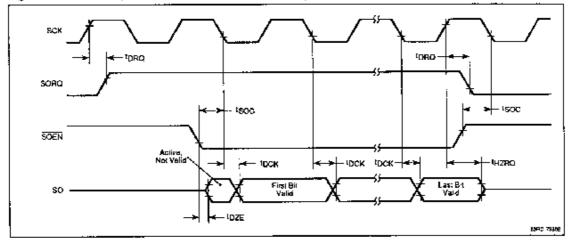

Figure 7 shows serial output timing when  $\overline{\text{SOEN}}$  is asserted in response to SORQ when SCK is low. If  $\overline{\text{SOEN}}$  is held inactive until after SORQ is asserted, and then  $\overline{\text{SOEN}}$  is asserted while SCK is low ( $\overline{\text{SOEN}}$  should be held inactive until the period of  $t_{\text{CSO}}$  after the falling edge of SCK), SO will become active but not valid  $t_{\text{DZSC}}$  after the next rising edge of SCK. SO will become valid with the first bit  $t_{\text{DCK}}$  after the next falling edge of SCK for use by an external device at the subsequent rising edge of SCK.

Subsequent bits will be shifted out  $t_{\rm DCK}$  after subsequent falling edges of SCK for use at subsequent rising edges of SCK. The last bit to be shifted out will also follow this pattern and will be held valid  $t_{\rm HZRQ}$  after the corresponding rising edge of SCK at which it is to be used. SORQ will be held  $t_{\rm DRQ}$  after this same rising edge of SCK and then removed.  $\overline{\rm SOEN}$  should be released at least  $t_{\rm SOC}$  before the next falling edge of SCK.

#### Serial Output, Case 2

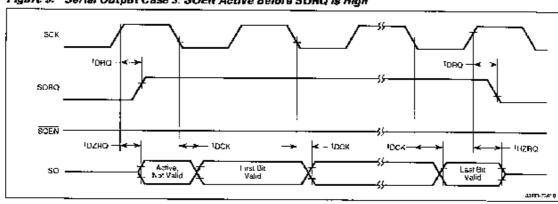

Figure 8 shows timing for serial output when SOEN is asserted in response to SORQ when SCK is high. If  $\overline{\text{SOEN}}$  is held inactive until after SORQ is asserted, and then SOEN is asserted while SCK is high (at least  $t_{\text{SOC}}$  before the falling edge of SCK), SO will become active but not valid  $t_{\text{OZE}}$  after the falling edge of SCK for use by an external device at the subsequent rising edge of SCK.

Note that although figure 8 shows  $\overline{\text{SOEN}}$  being asserted during a different SCK pulse than the one in which SORQ is asserted, it is permissible for these to occur during the same pulse of SCK as long as  $\overline{\text{SOEN}}$  is still asserted  $t_{\text{SOC}}$  before the falling edge of SCK. The timing for the second through the last bits is identical to the timing shown in figure 7.

#### Serial Output, Case 3

Figure 9 shows output timing when  $\overline{SOEN}$  is active before SORQ is high. If  $\overline{SOEN}$  is held active before SORQ is high, data will be shifted out whenever it becomes available in the serial output register (assuming previous data is already shifted out). In this case, SORQ will rise  $t_{DRQ}$  after a rising edge of SCK. SO will become active (but not valid yet)  $t_{DZRQ}$  after the same rising edge of SCK. The first valid SO bit occurs  $t_{DCK}$  after the next falling edge of SCK for use by an external device at the subsequent rising edge of SCK.

Subsequent bits will be shifted out  $t_{DCK}$  after subsequent falling edges of SCK for use at subsequent rising edges of SCK. The fast bit to be shifted out will also follow this pattern and will be held valid  $t_{HZRO}$  after the corresponding rising edge of SCK at which it is to be used. SORQ will be held  $t_{DRO}$  after this same rising edge of SCK and then removed.

Figure 7. Serial Output Case 1: SOEN Asserted in Response to SORQ When SCK is Low

Figure 8. Serial Output Case 2: SOEN Asserted in Response to SORQ When SCK is High

Figure 9. Serial Output Case 3: SOEN Active Before SORQ is High

## Serial Output, Case 4A

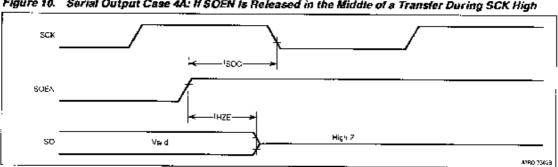

Avoid refeasing SOEN in the middle of a transfer (that is, before the last bit is shifted out), since this will stop the output shift operation. When SOEN is again asserted, the remainder of the transfer will be shifted out before the next transfer can begin. The next transfer will begin immediately without any indication of the byte/word boundary. If SOEN is released while SCK is high (figure 10) at least t<sub>SCC</sub> before the falling edge of SCK, then SO will go inactive t<sub>HZE</sub> after SOEN is released (which may be before or after the falling edge of SCK).

### Serial Output, Case 4B

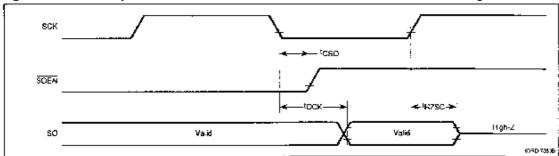

If SOEN is released while SCK is low (figure 11) at least 1<sub>CSO</sub> after the falling edge of SCK, then the next bit will be shifted out took efter the falling edge of SCK for

useat the subsequent rising edge of SCK, SO will then go inactive t<sub>HZSC</sub> after this rising edge of SCK.

Note: For all its uses,  $\overline{\mathrm{SOEN}}$  must not change state within tacc before or toso after the falling edge of SCK otherwise, the results will be indeterminate.

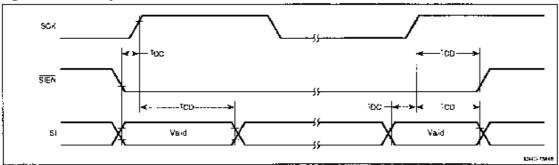

#### Serial Input

Serial input timing (figure 12) is much simpler than serial output timing. Data bits are shifted in on the rising edge of SCK if SIEN is asserted. Both SIEN and SI must be stable at least t<sub>DC</sub> before and t<sub>CD</sub> after the rising edge of SCK; otherwise the results will be indeterminate.

Figure 10. Serial Output Case 4A: If SOEN Is Released in the Middle of a Transfer During SCK High

Figure 11. Serial Output Case 48: If SOEN is Released in the Middle of a Transfer During SCK Low

Figure 12. Serial Input

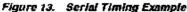

### Serial Timing Example

Figure 13 shows serial timing of cascaded SPIs with a common SCK, SO from the first SPI equals SI of the second, and the first SPI's SORQ Inverts to become SIEN of the second. SOEN of the first SPI is always asserted.

When cascading two SPIs in the described configuration, most of the timing involved is directly copied from the case of serial output with SOEN always enabled (figure 13). It must be shown that the results will be suitable for the serial input timing of the second SPI.

(1) SORQ(1) rises t<sub>DRD</sub> after a rising edge of SCK, and it is inverted (inverter has t<sub>PHL</sub> delay time) to become SIEN(2), which must be stable t<sub>DC</sub> before the next rising edge of SCK. It also must not change until t<sub>CD</sub> after this first rising edge of SCK as shown by case 2 in figure 8.

$$\begin{array}{l} t_{DRO} \ (\text{max}) + t_{PHL} \doteq t_{DC} \ (\text{min}) \leq t_{SCY} \ (\text{min}) \\ t_{PHL} \ (\text{max}) \leq t_{SCY} \ (\text{min}) - t_{DC} \ (\text{min}) - t_{DRO} \ (\text{max}) \\ \leq 480 - 55 - 150 \\ \leq 275 \ \text{ns} \ (\text{readily achieved by 74LS14,} \\ & \text{for example)} \end{array}$$

(2) SORQ(1) is released t<sub>DRQ</sub> after the last useful rising edge of SCK and Is Inverted (inverter has t<sub>PRL</sub> delay time) to become SIEN(2), which must remain stable t<sub>GD</sub> after the rising edge of SCK.

$$\begin{array}{ll} t_{DRQ} \; (min) \; + \; t_{PLH} \; (min) \; \geq \; t_{CD} \; (min) \\ t_{PLH} \; (min) \; \geq \; t_{CD} \; (min) \; - \; t_{DRQ} \; (min) \\ \; \geq \; 30 \; - \; 30 \\ \; \geq \; 0 \; (no \; problem, \; assuming \; causality) \end{array}$$

Note: This also shows  $t_{PH_{\infty}}$  (min)  $\gtrsim 0$  for the rising edge of SORQ.

(3) SO(1) is valid t<sub>DCK</sub> after a falling edge of SCK; since it becomes SI(2), it must be valid t<sub>DC</sub> before the next rising edge of SCK.

$$\begin{array}{l} t_{DCK} \mbox{ (max)} \ \div \ t_{DC} \mbox{ (min)} \ \le \ t_{SCK} \mbox{ (min)} \\ 150 \ - \ 55 \ \le \ 230 \ \mbox{ (this condition is satisfied)} \end{array}$$

(4) SO(1) remains valid t<sub>HZRQ</sub> after the last useful rising edge of SCK; since it becomes SI(2), it must remain valid t<sub>CD</sub> after this rising edge of SCK.

$t_{HZRQ}$  (min)  $\geq t_{CO}$  (min) 70  $\geq$  30 (this condition is satisfied)

Note: The above calculations may need to be adjusted for rise and fall times, since t<sub>SCY</sub> and t<sub>SCK</sub> are measured for midpoints of wave stopes.

### μPD77P20 UV ERASABLE EPROM VERSION

#### **Function**

The 77P20 operates from a single +5-volt power supply and can accordingly be used in any 77C20A/7720A masked ROM application.

### Use of Evakit-7720

The following sections describe electrical conditions that are required for programming the 77P20. However, the Evakit-7720, NEC's hardware emulator development tool for the 77C20A/7720A/77P20, meets the electrical and timing specifications presented below. When the Evakit-7720 is used for programming 77P20, all data transfers and formatting are handled automatically by Evakit's monitor program. Please refer to the Evakit-7720(B) User's Manual for programming procedures.

The information presented below in the sections on Configuration, Operation, and Programming (and the various subsections) is required only for users who do NOT intend to use an Evakit to program the 77P20.

### Configuration

Data transfer for programming and reading the internal ROM is partitioned into three bytes for each 23-bit wide instruction location and into two bytes for each 13-bit wide data location. Partitioning of data transfer Into and out of the data port is shown in figure 14.

Figure 14. Instruction ROM Format

|    | MSB |    |    |    |    |    |    |    |    |    |     |   |

|----|-----|----|----|----|----|----|----|----|----|----|-----|---|

|    | 22  | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12  |   |

|    |     |    |    |    |    |    |    |    |    |    |     |   |

|    |     |    |    |    |    |    |    |    |    |    | L9B |   |

| 15 | 10  | Э  | 8  | 7  | 6  | 5  | 4  | s  | 2  | 1  | ٥   | l |

#### Instruction ROM

The instruction ROM data is transferred through the data port as a high byte, middle byte, and low byte as shown in figure 15. Bit 7 of the middle byte should be assigned a value of zero. Data is presented to the data port in a bit-reversed format. The LSB through the MSB of an instruction ROM byte is applied to the MSB through the LSB of the data port, respectively.

#### Data ROM

Figure 16 shows the data ROM format. The data ROM data is transferred through the data port as a low byte and a high byte as shown in Figure 17. Bits 0, 1, and 2 of the low byte should be assigned a value of zero. Data is presented to the data port in corresponding order. The MSB through the LSB of a data ROM byte is applied to the MSB through the LSB of the data port, respectively.

initially and after each crasure, all bits of the 77P20 are in the zero state.

Figure 15. Transfer of Instruction ROM Data

| Oota Port   | 7       | 6      | 5     | 4    | 3  | ·2 | 1  | a  |

|-------------|---------|--------|-------|------|----|----|----|----|

| High Byte   | :5      | 16     | 17    | 18   | 19 | 23 | 21 | 22 |

|             |         |        |       |      |    |    |    |    |

| Middle Byte | *       | 8      | 9     | 10   | 11 | 12 | 13 | 14 |

|             |         |        |       |      |    |    |    |    |

| Low Byte    | 0       | 1      | 2     | 3    | 4  | 5  | ę  | 7  |

|             | * Set I | 0 D as | dummy | data |    |    |    |    |

Figure 16. Data ROM Format

| MSB |    |    |   |   |   |   |   |   |   |   |   | LSB |

|-----|----|----|---|---|---|---|---|---|---|---|---|-----|

| 12  | 11 | 10 | 9 | е | 7 | 9 | ō | 4 | 3 | 2 | 1 | Q   |

| Figure 17. | Tra.     | nster | of D   | eta A | OM C | ata |   |   |

|------------|----------|-------|--------|-------|------|-----|---|---|

| Date Port  | 7        | €     | 5      | 4     | 3    | 2   | 1 | 0 |

| High Byte  | 12       | 11    | 10     | ş-    | 8    | 7   | б | 5 |

|            |          |       |        |       |      |     |   |   |

| Low Byte   | 4        | Э     | 2      | 1 _   | 0    | +   | * | • |

|            | * Set to | O ps  | dumr•y | data. |      |     |   |   |

### **Operating Modes**

In order to read or write the instruction or data ROMs, the mode of operation of the 77P20 must be initially set. At the RST trailing edge, the  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , and  $\overline{\text{CS}}$  should be logical zero and the  $\overline{\text{DACK}}$ ,  $A_0$ , and SI signals should be set to determine the mode of operation accordingly, as set out in table 14.

Table 14. µPD77P20 Operation Mode

| DACK | Α <sub>0</sub> | Şì |                                     |

|------|----------------|----|-------------------------------------|

| 0    | O              | 0  | Write mode Instruction and data ROM |

| D    | G              | 1  | Read the instruction ROM            |

| 0    | 1              | ٥  | Read the data ROM                   |

Once set, the 77P20 will remain in the selected mode, A reset is required to transfer to another mode.

#### Write Mode

The individual instruction ROM and data ROM bytes are specified by control signals  $\overline{RD}$ ,  $A_0$ , SI, and INT as set out in table 15. Before writing the EPROM location, the bytes should be loaded accordingly.

Table 15. Write Mode Specification of ROM Bytes

| RD | AD | SI | 1 <b>N</b> T |                                |

|----|----|----|--------------|--------------------------------|

| 1  | 0  | 0  | 1            | Write instruction byte, frigh  |

| 1  | 0  | 1  | 0            | Write Instruction byte, middle |

| 1  | 0  | 1  | •            | Write instruction byte, low    |

| 1  | 1  | 3  | o            | Write cats byte, low           |

| 1  | 1  | 0  | 1            | Write cata byte, high          |

#### Read Mode

The instruction ROM and data ROM bytes are specified by the control signals  $\overline{RD}$ ,  $A_0$ , SI, and INT as set out in table 16. Reading is accomplished by setting the control signals accordingly.

Table 16. Read Mode Specification of ROM Bytes

| ĦŪ  | A <sub>0</sub> | SI | INT |                               |

|-----|----------------|----|-----|-------------------------------|

| C . | 0              | 0  | 1   | Road instruction byte, high   |

| С   | 0              | 1  | 0   | Fead instruction byte middle  |

| G   | 0              | 1  | 1   | Fead instruction byte, low    |

| 1   | 0              | 0  | 0   | Field data byte, high and low |

The instruction ROM and data ROM are addressed by the 9-bit program counter and the 9-bit ROM pointer respectively. The PC is reset to 000H and is automatically incremented to the end address 1FFH. The RP is reset to 1FFH and is automatically decremented to 000H.

#### Erasing

Programming can occur only when all data bits are in an erased or low (0) level state. Erase 77P20 programmed data by exposing it to light with wavelengths shorter than approximately 4000 angstroms. Note that constant exposure to direct sunlight or room level fluorescent flighting could erase the 77P20. Consequently, if the 77P20 will be exposed to these types of lighting conditions for long periods of time, mask its window to prevent unintentional erasure.

The recommended erasure procedure for the 77P20 is exposure to ultraviolet light with wavelength of 2537 angstroms. The integrated dose (i.e., UV intensity x exposure time) for erasure should not be less than 15 W-s/cm². The erasure time is approximately 20 minutes using an ultraviolet lamp with a power rating of 12,000 µW/cm².

During erasure, place the 77P20 within 1 inch of the lamp tubes. If the lamp tubes have filters, remove the filters before erasure.

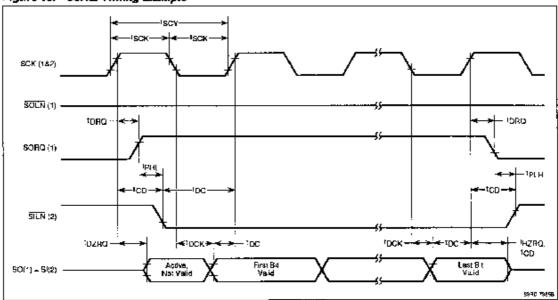

### Programming

Programming of the 77P20 Is achieved with a single 50-ms TTL pulse. Total programming time for the 11,776 bits of instruction EPROM and also for the 6630 bits of data EPROM is 26 seconds. Data is entered by programming a high level in the chosen bit locations. Both instruction ROM and data ROM should be programmed since they cannot be erased independently. Both instruction ROM and data ROM programming modes are entered in the same manner.

The device must be reset initially before it can be placed into the programming mode. After reset, the  $\overline{WR}$  signal and all other inputs (RD, CS/PROG,  $\overline{DACK}$ , A<sub>0</sub>, S1, and INT) should be a TTL low signal t<sub>RS</sub> prior to the falling edge of RST,  $\overline{WR}$  is then held for t<sub>RM</sub> before being

set to a TTL high-level signal. The device is now in a programming mode and will stay in this mode, allowing ROM locations to be sequentially programmed.

Programming Mode of Instruction ROM. Instruction ROM locations are sequentially programmed from address 000H to address 1FFH. The location address is incremented by the application of CLK for a duration of t<sub>CY</sub>. Data bytes for each location as specified by control signals  $\overline{\text{HD}}$ ,  $A_0$ , SI, and INT (table 15) are clocked into the device by the falling edge of  $\overline{\text{RD}}$ .

After the three bytes have been loaded into the device,  $V_{PP}$  is raised to 21 V ±0.5 V,  $t_{VS}$  prior to  $\overline{CS}/PROG$  transitioning to a TTL high-level signal.  $V_{PP}$  is held for the duration of  $t_{PRPR}$  plus  $t_{PRV}$  before returning to the  $V_{CC}$  level. After  $t_{PROL}$ , the instruction ROM address can be incremented to program the next location. Figure 18 shows the programming mode of instruction ROM timing.

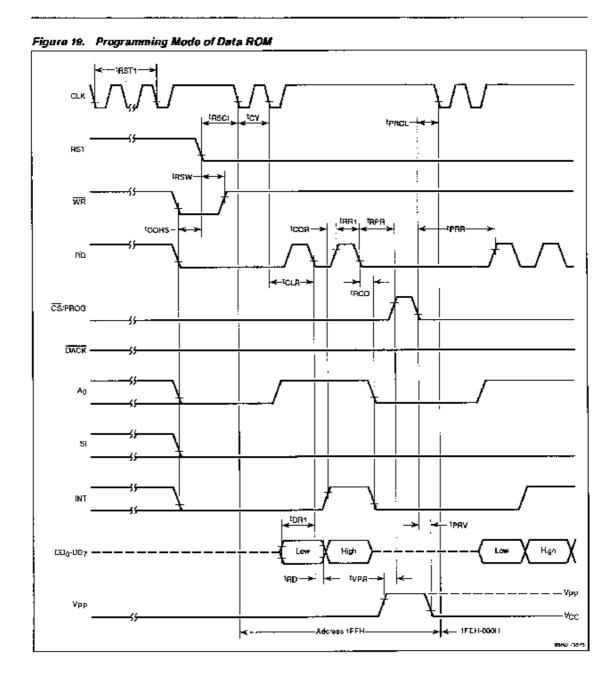

Programming Mode of Data ROM. Data ROM locations are sequentially programmed from address 1FFH to address 000H. The location address is decremented by the application of CLK for  $t_{\rm CY}$ . The data bytes for each location as specified by control signals  $\overline{\rm RD}$ ,  $A_0$ , SI, and INT are clocked into the device by the falling edge of  $\overline{\rm RD}$

After the two bytes have been loaded into the device,  $V_{PP}$  is raised to 21 V,  $\pm 0.5$  V  $t_{VPR}$  prior to  $\overline{CS/PROG}$  transitioning to a TTL high-level signal.  $V_{PP}$  is held for the duration of  $t_{PRPR}$  plus  $t_{PRV}$  before returning to the  $V_{CC}$  level. After  $t_{PRCL}$ , the data ROM address can be decremented to program the next location. Figure 19 shows programming mode of data ROM timing.

**Read Mode.** A read should be performed to verify that the data was programmed correctly. Prior to entering read mode, the device must be reset.

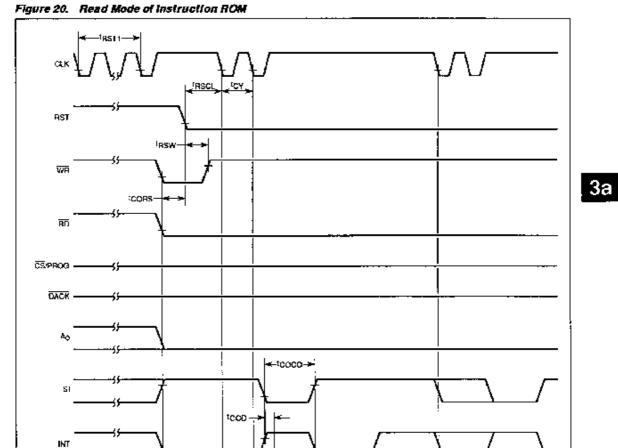

Read Mode of Instruction ROM. This mode is entered by holding the  $\overline{WR}$  signal at a TTL low level with the SI signal at a TTL high level and all other specified inputs  $(\overline{RD}, \overline{CS}/PROG, \overline{DACK}, A_0, \overline{INT})$  at TTL low levels for  $t_{CGRS}$  prior to the falling edge of RST.  $\overline{WR}$  is then held for  $t_{RSW}$  before being set to a TTL high level. The device is now in the instruction ROM read mode and will stay in this mode until reset.

Instruction ROM locations are sequentially read from address 000H through 1FFH. Application of CLK for  $t_{\rm CV}$  will increment the location address. The three data bytes will be read as specified by the control signals  $\overline{\rm RD}_1$  A<sub>0</sub>, SI, and INT (table 16). Figure 20 shows read mode of instruction ROM timing.

1CLD

80°D-7868

- 001H 1FFH

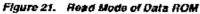

Read Mode of Data ROM. Figure 21 shows read mode of data ROM timing. This mode is entered by holding the WR signal at a TTL low level with the  $A_0$  signal at a TTL high level and all other specified inputs  $\langle \overline{RD}, \overline{CS}/PROG, \overline{DACK}, SI, INT\rangle$  at  $\overline{TTL}$  low levels for  $t_{CORS}$  prior to the falling edge of RST.  $\overline{WR}$  and  $A_0$  are then held for  $t_{CORS}$  prior to the falling edge of RST.  $\overline{WR}$  and  $A_0$  are then held for  $t_{RSW}$  before being set to a TTL high level

and TTL low level, respectively. The device is now in the data ROM read mode and will stay in this mode until it is reset.

Data ROM locations are sequentially read from address 1FFH through 000H. Application of CLK for  $t_{\rm CY}$  will decrement the location address. After the address has been decremented, the low byte of the current location

will be available at the data port subsequent to a  $t_{CLD}$  delay. Application of  $\overline{AD}$  will present the high byte  $t_{RD1}$  from the falling edge of the  $\overline{AD}$  pulse.  $\overline{AD}$  is then applied for  $t_{RV1}$  to complete reading of the current location.

### Read Operation, AC Characteristics

$T_A = 25^{\circ}C \pm 5^{\circ}C; V_{CC} = 5 \text{ V} \pm 5\%; V_{PP} = V_{CC} = 0.25 \text{ V} \text{ max}; V_{PP} = V_{CC} = 0.85 \text{ V} \text{ min}$

| Parameter                        | Symbol            | Min | Max | Ųnit | Conditions |

|----------------------------------|-------------------|-----|-----|------|------------|

| Data access time from<br>CLK     | told              |     | 1   | μ\$  |            |

| Date delay time from<br>St, IN 1 | tçop              |     | 1   | 5/2  |            |

| Data flot time from SI,<br>[N †  | <sup>†</sup> CODF | e   |     | ns   |            |

| St, INT pulse width              | topon             | 1   |     | gue  |            |

| PD recovery time                 | t <sub>RV1</sub>  | 500 | • • | ns   |            |

| Oate access time from<br>웨이나     | tRD:              |     | 150 | ne   |            |

| Data float time from AD *        | toFi              | 10  |     | ne   |            |

## Programming Operation, AC Characteristics